Quantum computing is a devilishly advanced know-how, with many technical hurdles impacting its improvement. Of those challenges two vital points stand out: miniaturization and qubit high quality.

IBM has adopted the superconducting qubit highway map of reaching a 1,121-qubit processor by 2023, resulting in the expectation that 1,000 qubits with at present’s qubit kind issue is possible. Nonetheless, present approaches would require very massive chips (50 millimeters on a facet, or bigger) on the scale of small wafers, or the usage of chiplets on multichip modules. Whereas this method will work, the goal is to realize a greater path towards scalability.

Now researchers at MIT have been capable of each scale back the scale of the qubits and carried out so in a manner that reduces the interference that happens between neighboring qubits. The MIT researchers have elevated the variety of superconducting qubits that may be added onto a tool by an element of 100.

“We’re addressing each qubit miniaturization and high quality,” stated William Oliver, the director for the Heart for Quantum Engineering at MIT. “In contrast to standard transistor scaling, the place solely the quantity actually issues, for qubits, massive numbers usually are not ample, they need to even be high-performance. Sacrificing efficiency for qubit quantity isn’t a helpful commerce in quantum computing. They have to go hand in hand.”

The important thing to this massive enhance in qubit density and discount of interference comes right down to the usage of two-dimensional supplies, particularly the 2D insulator hexagonal boron nitride (hBN). The MIT researchers demonstrated that a couple of atomic monolayers of hBN might be stacked to kind the insulator within the capacitors of a superconducting qubit.

Identical to different capacitors, the capacitors in these superconducting circuits take the type of a sandwich through which an insulator materials is sandwiched between two steel plates. The massive distinction for these capacitors is that the superconducting circuits can function solely at extraordinarily low temperatures—lower than 0.02 levels above absolute zero (-273.15 °C).

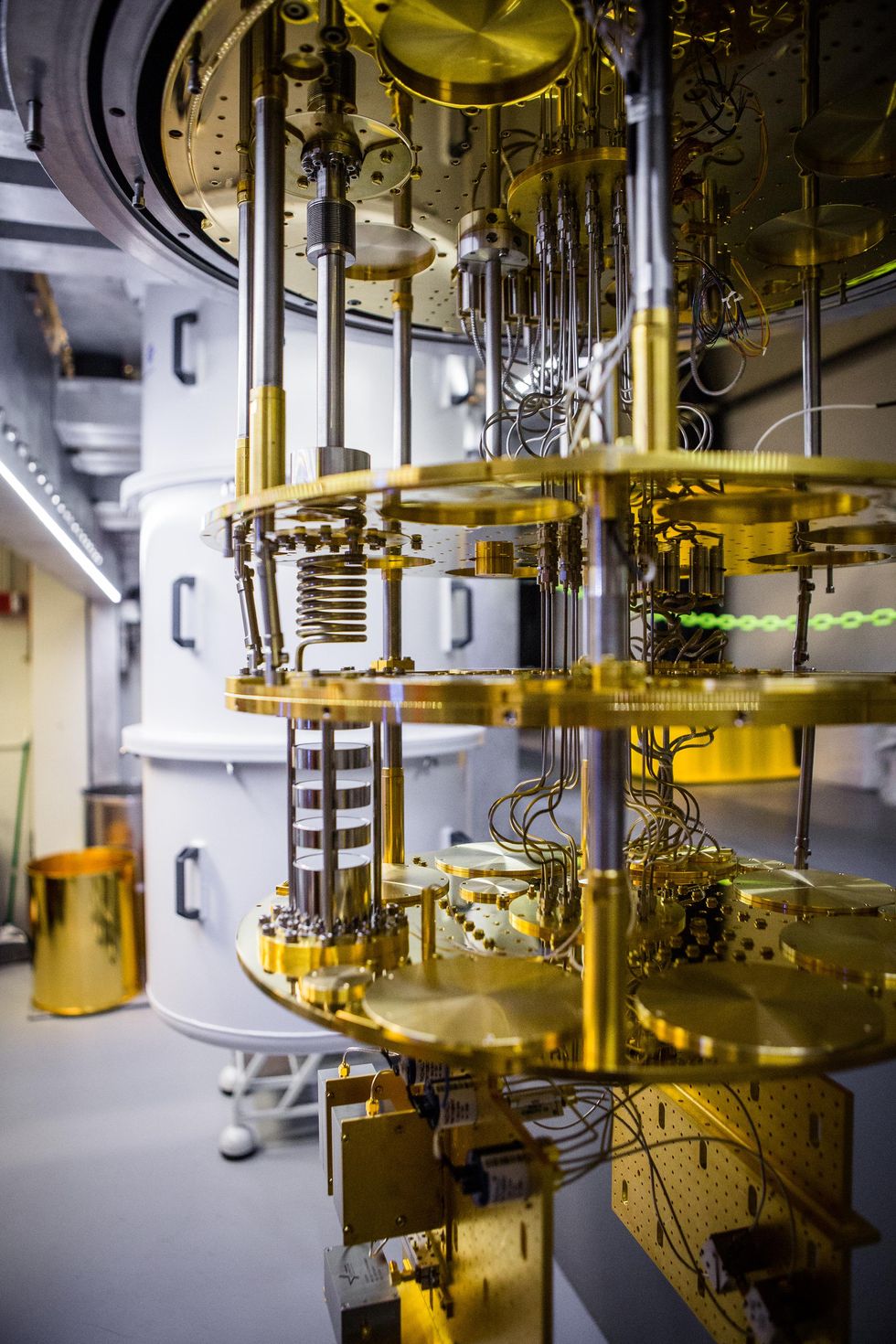

Superconducting qubits are measured at temperatures as little as 20 millikelvin in a dilution fridge.Nathan Fiske/MIT

Superconducting qubits are measured at temperatures as little as 20 millikelvin in a dilution fridge.Nathan Fiske/MIT

In that surroundings, insulating supplies which might be accessible for the job, comparable to PE-CVD silicon oxide or silicon nitride, have fairly a couple of defects which might be too lossy for quantum computing functions. To get round these materials shortcomings, most superconducting circuits use what are known as coplanar capacitors. In these capacitors, the plates are positioned laterally to at least one one other, reasonably than on prime of each other.

Consequently, the intrinsic silicon substrate beneath the plates and to a smaller diploma the vacuum above the plates function the capacitor dielectric. Intrinsic silicon is chemically pure and due to this fact has few defects, and the massive measurement dilutes the electrical subject on the plate interfaces, all of which ends up in a low-loss capacitor. The lateral measurement of every plate on this open-face design finally ends up being fairly massive (usually 100 by 100 micrometers) as a way to obtain the required capacitance.

In an effort to maneuver away from the massive lateral configuration, the MIT researchers launched into a seek for an insulator that has only a few defects and is appropriate with superconducting capacitor plates.

“We selected to review hBN as a result of it’s the most generally used insulator in 2D materials analysis as a consequence of its cleanliness and chemical inertness,” stated colead writer Joel Wang, a analysis scientist within the Engineering Quantum Programs group of the MIT Analysis Laboratory for Electronics.

On both facet of the hBN, the MIT researchers used the 2D superconducting materials, niobium diselenide. One of many trickiest features of fabricating the capacitors was working with the niobium diselenide, which oxidizes in seconds when uncovered to air, based on Wang. This necessitates that the meeting of the capacitor happen in a glove field full of argon gasoline.

Whereas this is able to seemingly complicate the scaling up of the manufacturing of those capacitors, Wang doesn’t regard this as a limiting issue.

“What determines the standard issue of the capacitor are the 2 interfaces between the 2 supplies,” stated Wang. “As soon as the sandwich is made, the 2 interfaces are “sealed” and we don’t see any noticeable degradation over time when uncovered to the ambiance.”

This lack of degradation is as a result of round 90 p.c of the electrical subject is contained throughout the sandwich construction, so the oxidation of the outer floor of the niobium diselenide doesn’t play a major position anymore. This finally makes the capacitor footprint a lot smaller, and it accounts for the discount in cross discuss between the neighboring qubits.

“The principle problem for scaling up the fabrication would be the wafer-scale development of hBN and 2D superconductors like [niobium diselenide], and the way one can do wafer-scale stacking of those movies,” added Wang.

Wang believes that this analysis has proven 2D hBN to be a great insulator candidate for superconducting qubits. He says that the groundwork the MIT workforce has carried out will function a highway map for utilizing different hybrid 2D supplies to construct superconducting circuits.